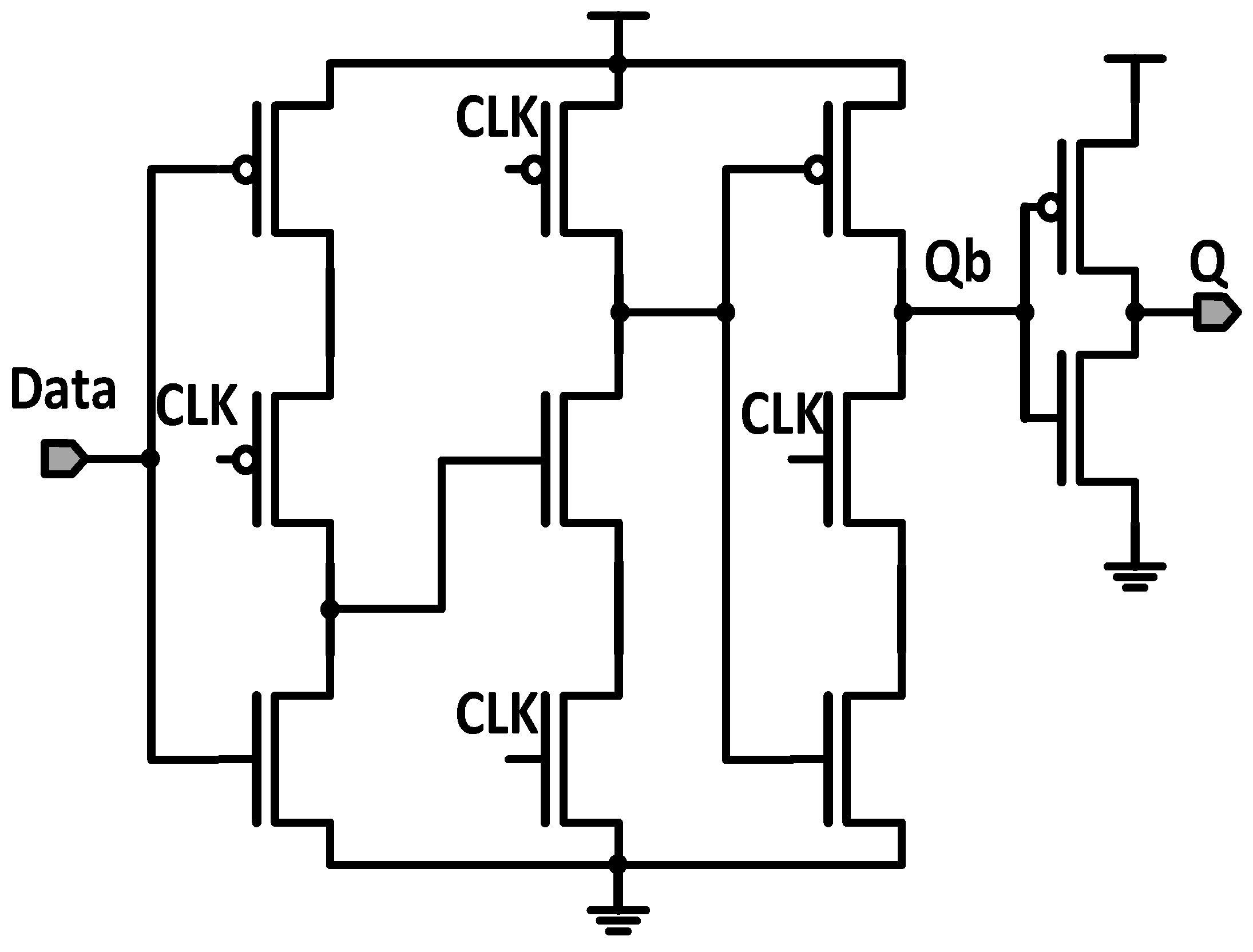

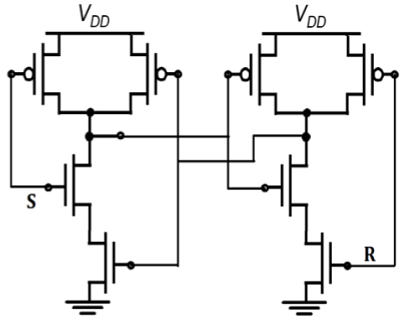

![PDF] Design of a Low-Power High-Speed T-Flip- Flop Using the Gate-Diffusion Input Technique | Semantic Scholar PDF] Design of a Low-Power High-Speed T-Flip- Flop Using the Gate-Diffusion Input Technique | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/546bbc334a9636e1c4ea48cebac0f25ed122729d/2-Figure4-1.png)

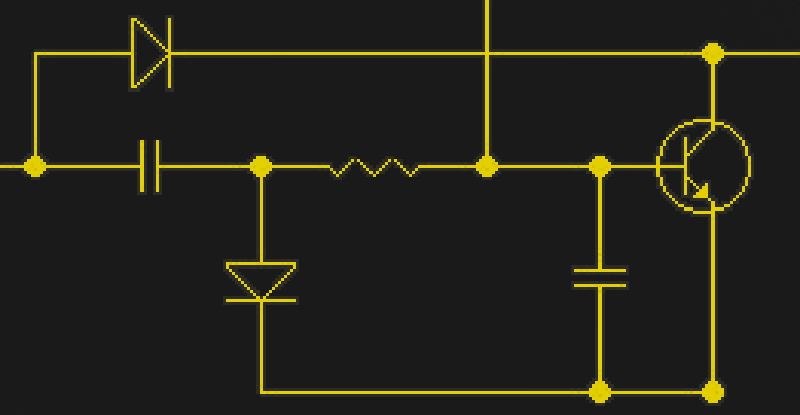

PDF] Design of a Low-Power High-Speed T-Flip- Flop Using the Gate-Diffusion Input Technique | Semantic Scholar

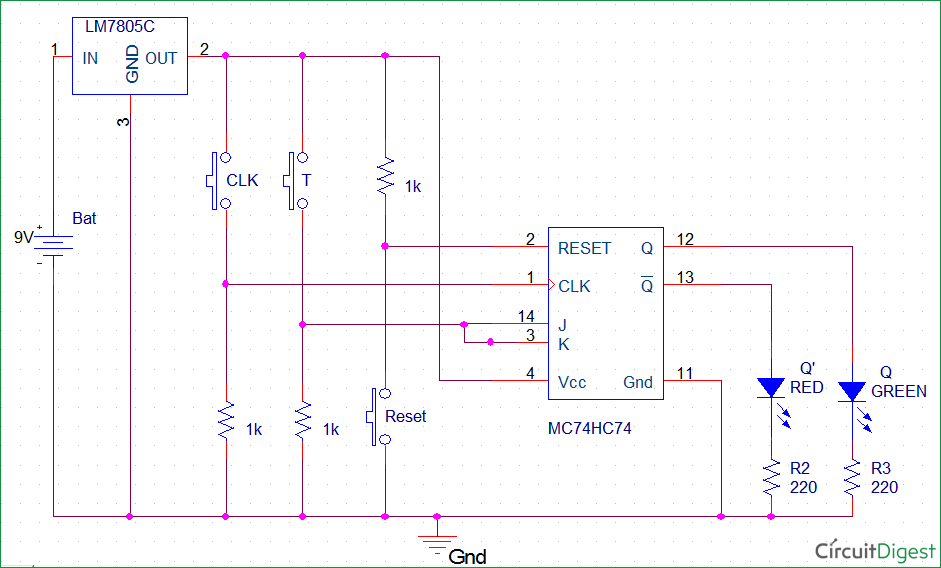

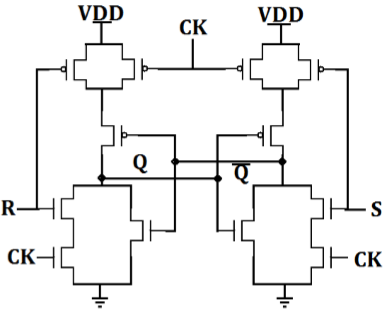

Figure 1 from A NOVEL DESIGN OF COUNTER USING TSPC D FLIP-FLOP FOR HIGH PERFORMANCE AND LOW POWER VLSI DESIGN APPLICATIONS USING 45 NM CMOS TECHNOLOGY Ms . | Semantic Scholar

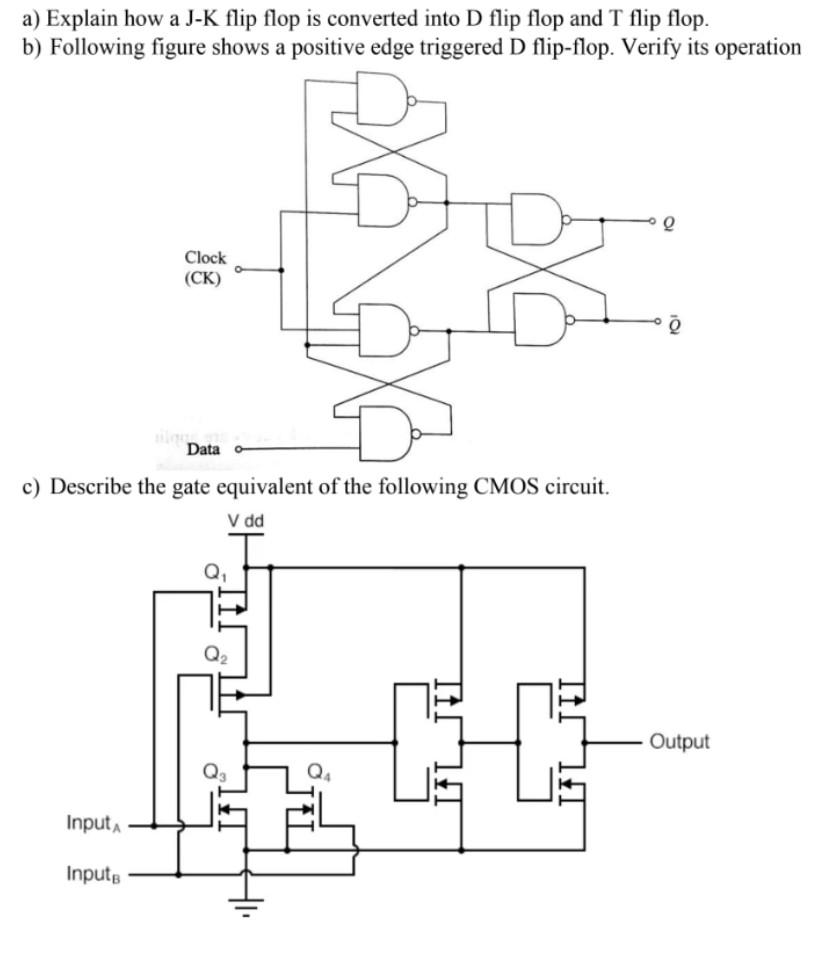

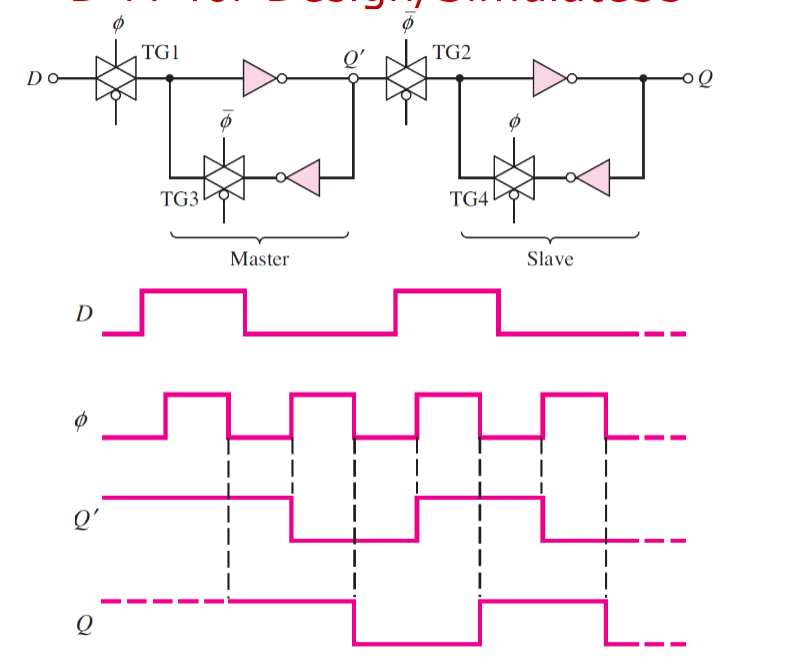

![Implement D flip-flop using Static CMOS. What are other design methods for it? [10] OR Draw D flipflop using CMOS and explain the working. Implement D flip-flop using Static CMOS. What are other design methods for it? [10] OR Draw D flipflop using CMOS and explain the working.](https://i.imgur.com/ksiy7VH.png)

Implement D flip-flop using Static CMOS. What are other design methods for it? [10] OR Draw D flipflop using CMOS and explain the working.

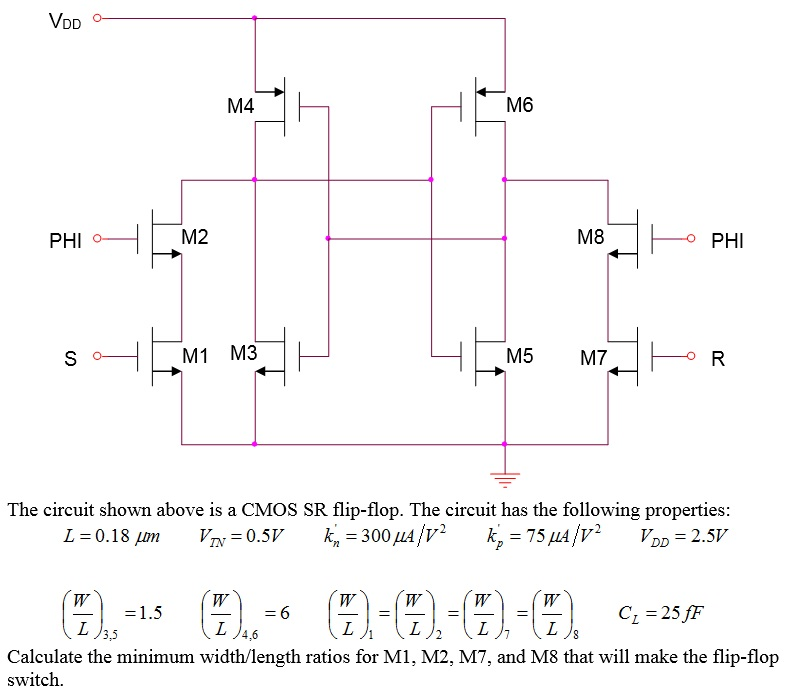

Design and analysis of ultra‐low power 18T adaptive data track flip‐flop for high‐speed application - Kumar Mishra - 2021 - International Journal of Circuit Theory and Applications - Wiley Online Library