Electronics | Free Full-Text | Delta-Sigma Modulator with Relaxed Feedback Timing for High Speed Applications

Figure 1 from Comparative analysis of D flip-flops in terms of delay and its variability | Semantic Scholar

FPGA sketch containing sampled-clock D flip-flop and sinc 2 decimator.... | Download Scientific Diagram

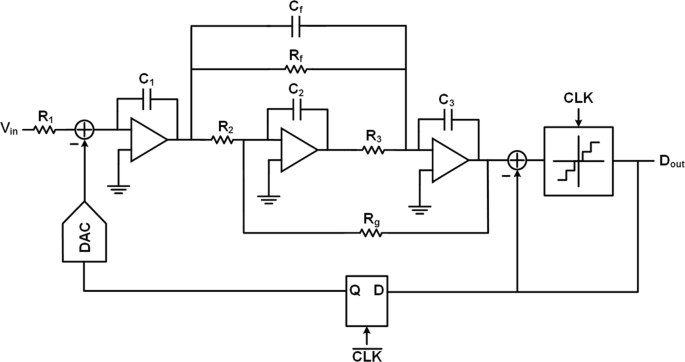

A 100-Mhz Bandwidth 80-dB Dynamic Range Continuous-Time Delta-Sigma Modulator with a 2.4-Ghz Clock Rate | Discover Nano

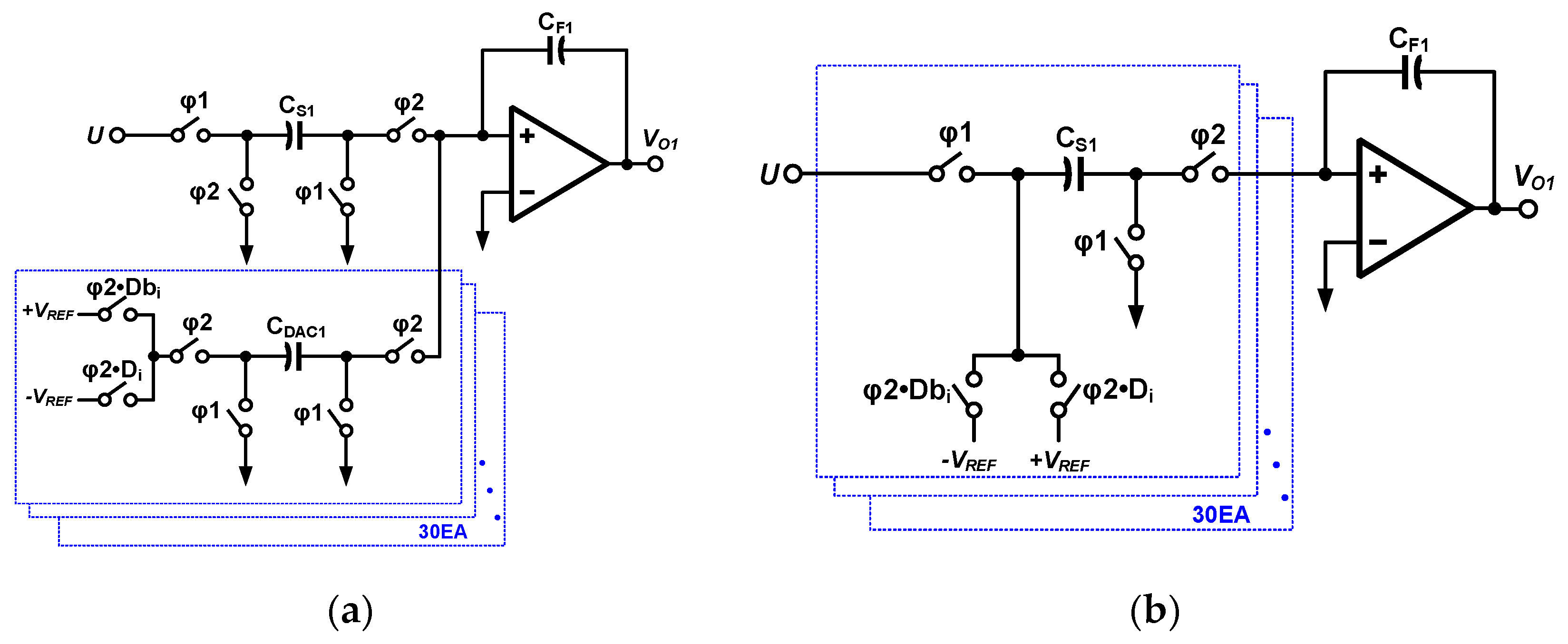

Electronics | Free Full-Text | 9.9 µW, 140 dB DR, and 93.27 dB SNDR, Double Sampling ΔΣ Modulator Using High Swing Inverter-Based Amplifier for Digital Hearing Aids

Figure 3 from Comparative analysis of D flip-flops in terms of delay and its variability | Semantic Scholar

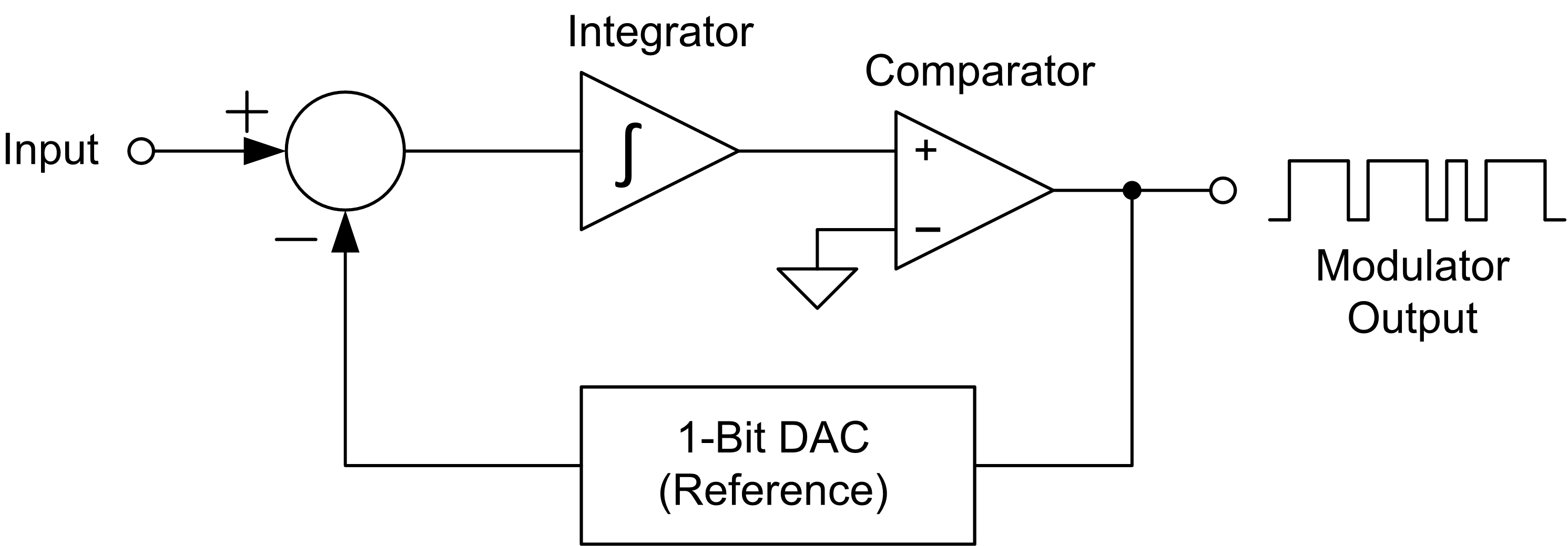

![Activity: Delta – Sigma Modulator [Analog Devices Wiki] Activity: Delta – Sigma Modulator [Analog Devices Wiki]](https://wiki.analog.com/_media/university/courses/alm1k/alm-signals-labs/alm-ss-lab-delta-sigma-fig_2.png?w=600&tok=e64ad2)

![Activity: Delta - Sigma Modulator [Analog Devices Wiki] Activity: Delta - Sigma Modulator [Analog Devices Wiki]](https://wiki.analog.com/_media/university/courses/electronics/a17_f2.png?w=600&tok=06bd09)

![PDF] FPGA based sigma – Delta analogue to digital converter design | Semantic Scholar PDF] FPGA based sigma – Delta analogue to digital converter design | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/5b8805f36995ecdaae0e294c2817b2b33dccc6c3/2-Figure1-1.png)

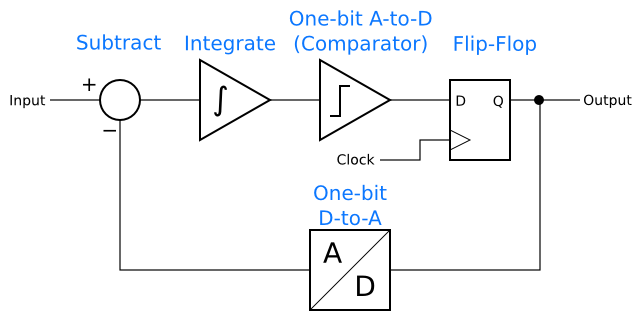

![Activity: Delta – Sigma Modulator [Analog Devices Wiki] Activity: Delta – Sigma Modulator [Analog Devices Wiki]](https://wiki.analog.com/_media/university/courses/alm1k/alm-signals-labs/alm-ss-lab-delta-sigma-fig_1.png?w=600&tok=4cf02f)